Описание сети в виде СМО

Рис.1. Структурная схема

При входе заявки в модель она поступает во входной буфер системы IN_BUF, где накапливаются по мере поступления. Далее заявки распределяются в 2 приёмных буфера процессоров первого сегмента системы. Распределение заявок происходит по критерию минимума входной очереди входных буферов. После обработки в первом сегменте заявка направляется во второй сегмент системы. Распределение заявок также происходит по критерию минимума входной очереди входных буферов. Далее заявка выводится из системы.

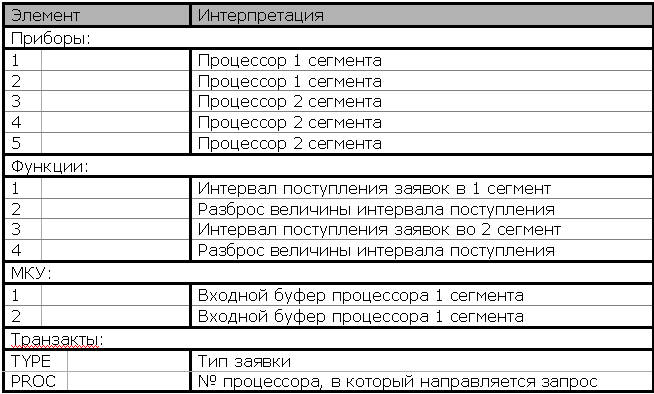

Таблица определений

Единица времени — 1 мкс.

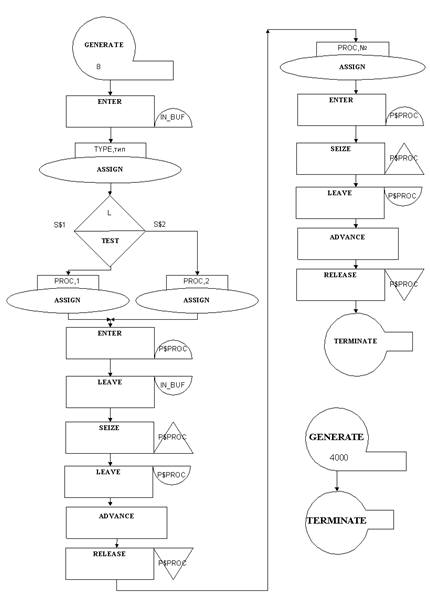

Блок-схема

Имитационный эксперимент

Текст программы

REAL XAC, 3000

SIMU

TYPE EQU 1

PROC EQU 2

COUNT EQU 3

IN_BUF EQU 6

1 FUNC P$TYPE,D2

1,14/2,17

2 FUNC P$TYPE,D2

1,4/2,6

3 FUNC P$TYPE,D2

1,22/2,25

4 FUNC P$TYPE,D2

1,10/2,5

1 STORAGE 10

2 STORAGE 10

7 VARI 2#(SC$6@3)

8 VARI 1+P$COUNT

GENE 8

ENTER IN_BUF

ASSI COUNT, V$7

ASSI TYPE, V$8

A TEST_E R$1, 0, B

TEST_E R$2, 0, A

B TEST_L S$1, S$2, C

ASSI PROC, 1

TRAN , D

C ASSI PROC, 2

D ENTER P$PROC

LEAVE IN_BUF

SEIZE P$PROC

LEAVE P$PROC

ASSI 4,FN$1

ASSI 5,FN$2

ADVA P$4, P$5

RELE P$PROC

TEST_LE S$3, S$4, E

TEST_LE S$3, S$5, F

ASSI PROC, 3

TRAN , G

E ASSI PROC, 4

TRAN , G

F ASSI PROC, 5

G ENTER P$PROC

SEIZE P$PROC

LEAVE P$PROC

ASSI 4,FN$3

ASSI 5,FN$4

ADVA P$4, P$5

RELE P$PROC

TERM

GENE 4000

TERM 1

START 1

END

Выходные данные

LINE BLOCK

1 REAL XAC, 3000

2 SIMU

3 *****

4 TYPE EQU 1

5 PROC EQU 2

6 COUNT EQU 3

7 IN_BUF EQU 6

8 *****

9 1 FUNC P$TYPE,D2

10 1,14/2,17

11 2 FUNC P$TYPE,D2

12 1,4/2,6

13 3 FUNC P$TYPE,D2

14 1,22/2,25

15 4 FUNC P$TYPE,D2

16 1,10/2,5

17 *****

18 1 STORAGE 10

19 2 STORAGE 10

20 *****

21 7 VARI 2#(SC$6@3)

22 8 VARI 1+P$COUNT

23 *****

24 *****

25 1 GENE 8

26 2 ENTER IN_BUF

27 *****

28 3 ASSI COUNT, V$7

29 4 ASSI TYPE, V$8

30 *****

31 5 A TEST_E R$1, 0, B

32 6 TEST_E R$2, 0, A

33 7 B TEST_L S$1, S$2, C

34 8 ASSI PROC, 1

35 9 TRAN , D

36 10 C ASSI PROC, 2

37 11 D ENTER P$PROC

38 12 LEAVE IN_BUF

39 13 SEIZE P$PROC

40 14 LEAVE P$PROC

41 15 ASSI 4,FN$1

42 16 ASSI 5,FN$2

43 17 ADVA P$4, P$5

44 18 RELE P$PROC

45 *****

46 19 TEST_LE S$3, S$4, E

47 20 TEST_LE S$3, S$5, F

48 21 ASSI PROC, 3

49 22 TRAN , G

50 23 E ASSI PROC, 4

51 24 TRAN , G

52 25 F ASSI PROC, 5

53 26 G ENTER P$PROC

54 27 SEIZE P$PROC

55 28 LEAVE P$PROC

LINE BLOCK

56 29 ASSI 4,FN$3

57 30 ASSI 5,FN$4

58 31 ADVA P$4, P$5

59 32 RELE P$PROC

60 33 TERM

61 *****

62 34 GENE 4000

63 35 TERM 1

64 START 1

65 END

SYMBOL VALUE SYMBOL VALUE

====== ===== ====== =====

A 5 B 7

C 10 COUNT 3

D 11 E 23

F 25 G 26

IN_BUF 6 PROC 2

TYPE 1

RELATIVE CLOCK 4000 ABSOLUTE CLOCK 4000

BLOCK COUNTS

BLOCK CURRENT TOTAL BLOCK CURRENT TOTAL BLOCK CURRENT TOTAL

1 1 500 2 0 499 3 0 499

4 0 499 5 0 499 6 0 0

7 0 499 8 0 242 9 0 242

10 0 257 11 0 499 12 2 499

13 0 497 14 0 497 15 0 497

16 0 497 17 2 497 18 0 495

19 0 495 20 0 326 21 0 165

22 0 165 23 0 169 24 0 169

25 0 161 26 5 495 27 0 490

28 0 490 29 0 490 30 0 490

31 3 490 32 0 487 33 0 487

34 1 2 35 0 1

FACILITY AVERAGE NUMBER AVERAGE SEIZING PREEMPTING

UTILIZATION ENTRIES TIME/TRAN TRANS.NO. TRANS.NO.

1 0.96 242 15.85 9

2 1.00 255 15.65 6

3 0.99 163 24.39 7

4 0.98 167 23.59 1

5 0.96 160 24.04 13

STORAGE CAPACITY AVERAGE AVERAGE ENTRIES AVERAGE CURRENT MAXIMUM

CONTENT UTILIZ. TIME/TR CONTENT CONTENT

1 10 0.00 0.06 242 9.71 0 2

2 10 1.00 0.11 257 17.05 2 3

3 32767 2.00 0.00 165 52.30 2 4

4 32767 1.00 0.00 169 46.60 2 3

5 32767 1.00 0.00 161 35.06 1 3

Заключение

Моделирование работы системы показало необходимые объёмы буфера системы и буферов процессоров. Максимальное содержимое входного буфера системы составляет 1 транзакт, для буферов процессоров второго сегмента оно равно 4, 3 и 3 соответственно. При выборе объема буферов можно сделать некоторый запас по объёму, например десятикратный. Тогда объёмы входного буфера системы и буферов первого сегмента конвеера будут равны 10, остальных — по 40. |